A/D and D/A CONVERSION/SAMPLING CIRCUITS

## App Note 111: Dual, Voltage-Output DAC Consumes Miniscule Power

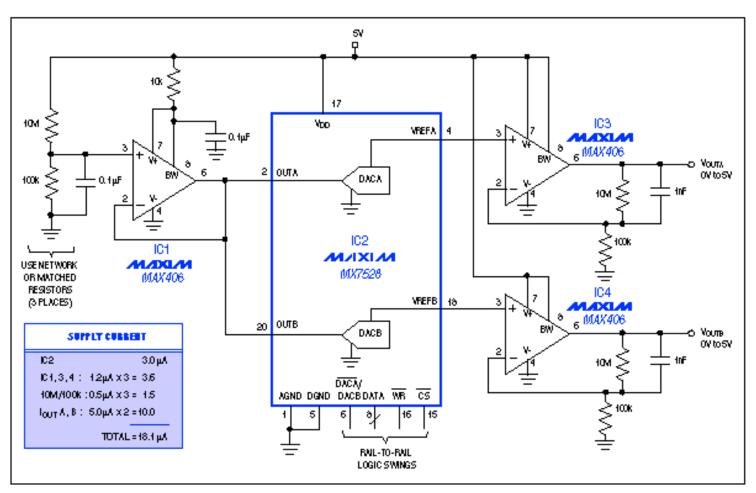

The dual, voltage-output DACs shown in the figure below employ a combination of power-conserving tricks to draw less than 20µA from a 5V supply. The circuit suits a need for programmable voltage generation in slow or static applications, such as the nulling of offsets in a micropower instrument.

Providing two independent 8-bit DACs with voltage outputs and a common reference, this dual-DAC circuit draws less than 20µA from a 5V supply.

Current-output DACs normally waste power by routing the complement of I<sub>OUT</sub> to ground. The circuit in the figure avoids wasting power by operating each DAC in the reverse voltage-switching mode, in which the reference voltage is applied to the pins normally labeled I<sub>OUT</sub>.

The OUT pins in this circuit have a constant and relatively low input impedance of  $11k\Omega$ . To reduce input currents, the reference voltage is divided by 100 (from 5V to 50mV) and therefore delivers only 5?A to each DAC input. Signal levels are restored by a compensating gain of 100 in each output amplifier. Inexpensive  $10M\Omega/100k\Omega$  resistor networks are a good choice for the multiple 100:1 attenuators required. Though only 2% accurate, their matching and tracking is much better than that of discrete resistors.

Greater scaling is impractical because of 0.5 mV (maximum) offsets in the output amplifiers shown. Amplified by 100, these offsets produce worst-case output errors of  $\pm 1\%$  (0.05V). The errors are constant over temperature, but additional error due to drift over a range of  $40^{\circ}\text{C}$  is typically  $\pm 1/2 \text{LSB}$ . The micropower output amplifiers shown in the figure were chosen for their low supply current—their typical IDD is only  $1\mu\text{A}$ .

The last requirement for minimizing the overall current drain is to ensure that logic signals applied to the digital inputs of IC1 swing to within 0.2V of each rail. The maximum specified IDD for that condition is 100µA over temperature, but this specification (like most CMOS IDD ratings) is extremely conservative. IDD is negligible for Rail-to-Rail swings but rises dramatically as the swings approach TTL levels.

A similar version of this article appeared in *Electronic Design* magazine.

## **More Information**

MAX406: QuickView -- Full (PDF) Data -- Free Samples

MX7528: QuickView -- Full (PDF) Data -- Free Samples

Sheet